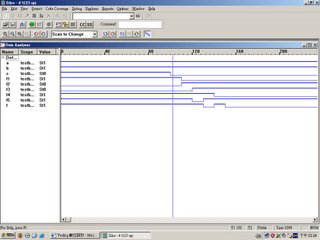

module top(a,b,c,f);

input a,b,c;

output f;

wire f1,f2,f3,f4,f5;

and #10 h1(f1,a,c);

not #10 h2(f2,c);

and #10 h3(f3,b,f2);

not #30 h4(f4,f2);

or #10 h5(f5,f3,f1);

and #10 h6(f,f5,f4);

endmodule

========================================

module testbench;

reg a,b,c;

wire f;

top a1(a,b,c,f);

initial

begin

#0 c=1; a=1;b=1;

#100 c=0;

#1000 $stop;

end

endmodule