module top;

reg Bin,clk,reset;

wire q0,q0_bar,q1,q1_bar,q11,q10,D1,bin_bar,b1,b2,b3,b4,Bout;

DFF m3(clk,q0_bar,reset,q0,q0_bar);

DFF m7(clk,D1,reset,q1,q1_bar);

nand #3 m1(bin_bar,Bin,Bin);

nand #3 m4(q11,q0_bar,q1);

nand #3 m5(q10,q0,q1_bar);

nand #3 m6(D1,q11,q10);

nand #3 m8(b1,q0_bar,q1,bin_bar);

nand #3 m9(b2,q1_bar,q0,bin_bar);

nand #3 m10(b3,q0,q1,Bin);

nand #3 m11(b4,q0_bar,q1_bar,Bin);

nand #3 m12(Bout,b1,b2,b3,b4);

initial

begin

clk=0;Bin=1;reset=0;

#20 reset=1;

#50 Bin=1;

#50 Bin=0;

#50 Bin=1;

#50 Bin=1;

#50 Bin=1;

#50 Bin=1;

#50 Bin=1;

#50 Bin=0;

#50 Bin=0;

#50 Bin=0;

#50 Bin=0;

#50 Bin=0;

#50 Bin=0;

#90 Bin=0;

#50 Bin=1;

#5000 $finish;

end

always

#28 clk=~clk;

endmodule

module DFF(clk,D,reset,Q,Q1);

input clk,D,reset;

wire a1,a2,a3,a4;

output Q,Q1;

nand q1(a1,a4,a2);

nand q2(a2,clk,reset,a1);

nand q3(a3,a2,clk,a4);

nand q4(a4,a3,reset,D);

nand q5(Q,a2,Q1);

nand q6(Q1,Q,reset,a3);

endmodule

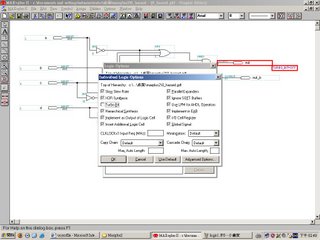

使用synapitiCAD執行結果如下圖

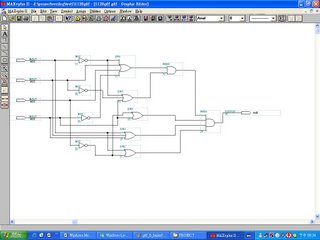

使用silos執行結果如下圖